Test 7

All Problems worth 20%.

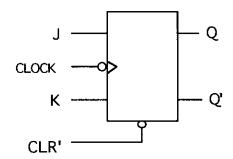

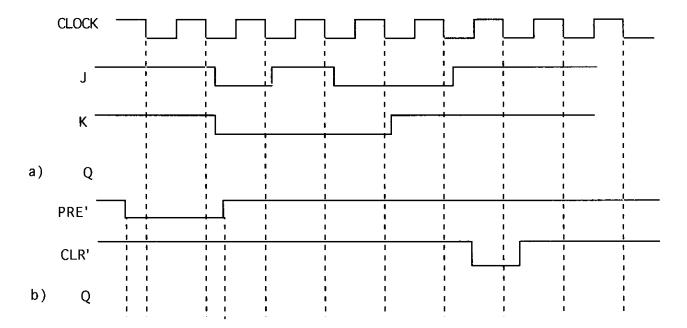

- 1. For the following JK trailing-edge triggered flip flop with an active low clear, show the timing diagram for Q.

- a) Assuming no PRE' or CLR' input.

- b) With the PRE' and CLR' inputs shown.

2. For the following state table, complete the timing trace as far as you can

| q <sub>1</sub> q <sub>2</sub> | q <sub>1</sub> * q <sub>2</sub> * |       | z     |       |

|-------------------------------|-----------------------------------|-------|-------|-------|

|                               | x = 0                             | x = 1 | x = 0 | x = 1 |

| 0.0                           | 0 1                               | 0 0   | 0     | 0     |

| 0 1                           | 10                                | 0 1   | 1     | 0     |

| 10                            | 00                                | 1 1   | 1     | 1     |

| 1 1                           | 1 0                               | 1 0   | 0     | 0     |

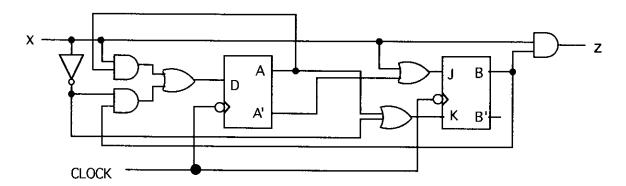

- 3. For the following circuit, complete the state table. (Decide if you need one or two columns for z.

| АВ  | A* B*     |     | Z |

|-----|-----------|-----|---|

|     | x = 0 $x$ | = 1 |   |

| 0 0 |           |     |   |

| 0 1 |           |     |   |

| 10  |           |     |   |

| 1 1 |           |     |   |

4. For the following state table, design a system using a JK flip flop for A, a D flip flop for B, and AND, OR and NOT gate. Show the flip flop input equations and the output equation; you do NOT need to draw a block diagram.

| АВ  | A* B* |      | Z    |      |

|-----|-------|------|------|------|

|     | x= 0  | x= 1 | x= 0 | x= 1 |

| 00  | 0 1   | 0 1  | 0    | 0    |

| 0 1 | 0 1   | 1 0  | 1    | 0    |

| 10  | 1 1   | 0 0  | 1    | 1    |

| 1 1 | 10    | 1 0  | 0    | 0    |

5. For the following state table and state assignment, design a system using an JK flip flop for  $q_1$  and a SR flip flop for  $q_2$ . Show the flip flop input equations and the output equation; you do NOT need to draw a block diagram.

| q | q     | *     | Z |

|---|-------|-------|---|

|   | x = 0 | x = 1 |   |

| Α | С     | В     | 0 |

| В | В     | Α     | 1 |

| С | Α     | В     | 1 |

| q | $q_1$ | $q_2$ |

|---|-------|-------|

| Α | 0     | 0     |

| В | 1     | 1     |

| С | 0     | 1     |