# UNLOCKING THE POWER OF BOUNDARY-SCAN

PCB Test & Programming Solutions

from the IEEE 1149.1 Boundary-Scan Experts

JTAG Technologies

www.jtag.com

# Test and In-System Programming Solutions for Today's Problems

Throughout the electronics industry, manufacturers turn to the latest device technologies, such as ball-grid arrays, chip-scale packages, and other small outlines, to provide the functionality and miniaturization they need. However, along with the benefits, the new packages increase the difficulty of accessing printed circuit boards (PCBs) for testing and on-board device programming.

Boards are becoming much more crowded, component complexity is increasing, and circuit performance issues are becoming more demanding. Industry has addressed these difficult access problems through adoption of the IEEE 1149.1 boundary-scan standard, which provides pin-level access—independent of the device packaging technology—to even the most crowded assemblies.

CPLD in BGA Package

Advanced products from JTAG Technologies deliver the power of boundary-scan in compliance with the IEEE standard. You'll achieve practical solutions that you can implement quickly, realizing immediate benefits and significant cost savings. Moreover, the JTAG Technologies solutions apply uniformly throughout your business, including your subcontractors, with a common platform for development, prototyping, production, and field service.

Company Background

JTAG Technologies is the world's foremost provider of comprehensive test and in-system programming solutions based on the IEEE Boundary-Scan standard 1149.1. Since our founding in 1993, we have continuously enhanced the value of boundary-scan applications with a stream of innovations and product improvements, based on the needs of the test community. We apply our industrial instrumentation expertise to the development of powerful engineering and production software, along with top-line boundary-scan hardware.

We maintain a highly experienced staff of development engineers and application engineers ready to support your needs world-wide. With thousands of systems in operation around the world, our engineers have delivered the highest quality solutions and services, everything from introductory training to the preparation of specific tests and programs to meet exacting customer requirements. A customer reference brochure is available that describes the successes that users have experienced with our technology.

Our corporate headquarters are in Eindhoven, The Netherlands, and we have offices in China, Finland, Sweden, the United Kingdom, and the United States. We're represented by a global network of authorized distributors and representatives throughout North America, Europe, Asia, the Middle East, South Africa and Australia.

## Practical and Powerful— Boundary-Scan from JTAG Technologies

Unlock the power of boundary-scan for your test and programming applications with the JTAG Technologies family of software tools and hardware controllers. You'll find it a simple matter to create your first application and to add new ones. Tests and in-system programming routines will be ready in time to help debug your first prototype, reducing your product's time-to-market. The same streamlining applies to handling design changes and product updates. Applications are easily ported between development and production, so as soon as they are verified in engineering, they can be used in your factory.

What has raised boundary-scan to this level of real-world practicality? JTAG Technologies' development and production systems provide your engineers and factory personnel with the assistance they need, simplifying their tasks and allowing them to concentrate on their mission, not the intricacies of boundary-scan. At the same time, the developer has access to the underlying test details,

enabling an expert user to manipulate and fashion applications for optimum performance. This dual level of user

interface is unique and highly beneficial to realizing boundary-scan's

tremendous power.

You can choose from a wide range of boundary-scan controllers, designed specifically for critical industrial applications. The high-performance, scalable controller types include USB, Ethernet, FireWire, PCI, PXI and CompactPCI interfaces. In addition, VXI, ISA, and PC parallel port versions are available as well as a variety of parallel I/O scan modules to enhance board testability.

# A Full Range of **Development Packages**

Development of applications for testing and PLD/Flash programming is based on the design's electronic netlist, boundary-scan description language (BSDL) files and device libraries. The process is streamlined thanks to our family of automated application generators. To simplify product selection, we've assembled the test and in-system programming software into a number of development packages. You choose the package that's right for your design or engineering environment and your application, optimizing your investment. Should your needs change, you can add individual software modules at any time.

For special applications that can't be covered by the automated generation tools, we offer extended flexibility with our High-level Scan Function Library (HSL). Examples of such applications are testing processor peripheral devices in complex clusters, testing digital/analog and analog/digital converters, mixed signal testing, testing thermal sensing devices on an I2C or SPI bus, reading board calibration data and storing in EPROM, and many more. The powerful HSL provides a set of DLL-based functions which may be called from C / C++ programming environments as used in functional test development.

#### The development packages provide:

- Support for Windows (98/NT/2000/XP) and UNIX (Solaris and HP-UNIX) platforms

- Node-locked versions for stand-alone use and floating licenses for shared use for Windows-based products

- Netlist converters to automate the path between your schematic design system and application development modules

- Support for system-level testing and in-system programming using devices from National Semiconductor, Texas Instruments, Lattice Semiconductor and Firecron

- Support for the optional JTAG Visualizer to check schematics and/or board layouts during the development process to assess boundary-scan design for testability (DFT)

## **Test Development**

#### Basic Test Development Package

The Basic Test Development Package is an entry-level system, well suited for applications involving less

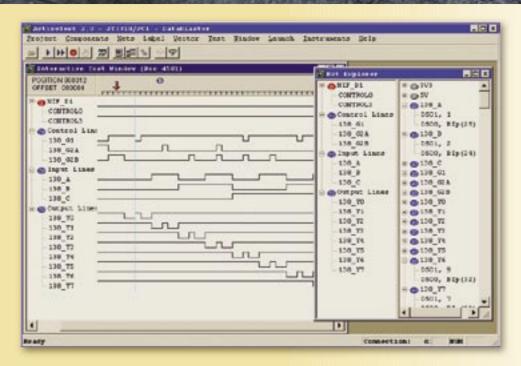

complex PCBs or for companies with a limited number of new designs. The Basic Package provides ActiveTest, an interactive software tool that allows you to create interconnect tests for non-boundary-scan portions of your design and to probe the board via the boundary-scan chain. Further, it includes automatic generation of test patterns for the boundary-scan infrastructure on your board and utilities for syntax and semantic checking of device BSDL files. Test failures are reported for analysis in a familiar net-oriented truth-table format. Since test generation is based on a netlist of the design, your tests can be ready before the prototypes come back from manufacturing.

#### Standard Test Development Package

Building on the interactive generation of test vectors, the Standard Package allows you to automate test develop-

ment for boundary-scan interconnections, including coverage for inverters, serial and pull-up/pull-down resistors, multiplexers, and buffers that reside between scan elements. The Standard Package also provides automatic generation of test patterns through or to board connectors. Test preparation time is reduced significantly, and full 100% coverage of the scan interconnections is achieved.

#### Full Test Development Package

The Full Test

Development Package

is ideal for companies

which produce highly

complex PCBs with

SRAM, DRAM and other types of memory arrays, and which desire the highest possible fault coverage and diagnostic resolution. This package contains all of our automatic vector generation tools including boundary-scan infrastructure, interconnections, memory interconnections, and the application of fault simulation vectors created on third-party tools for logic clusters. It enables you to move through test development rapidly, accommodating a large number of new designs at a consistently high quality level.

ActiveTest Graphical User Interface

#### Professional Test Development Package

This package contains all of our automatic test pattern generators plus the Boundary-scan Fault Coverage Examiner

(BFCE), allowing you to determine when all test requirements have been met. The combination of extensive pattern generation and coverage evaluation enables the R&D organization to operate at the highest quality level. The Professional Package can be an integral part of your company's **Total Quality Management** program. You will be able to rapidly evaluate test effectiveness during PCB development and make adjustments on the spot before problems occur in prototyping or later in production. If your company has adopted design-for-testability as an integral part of the design flow, the Professional Test Development Package will help you meet your high quality standards.

#### **Optimizing Your Test Strategy**

Boundary-scan is a good choice to improve a test strategy that, for example, includes functional testing for complex surface-mount designs. In these situations, use boundary-scan to pre-screen product for manufacturing faults, quickly weeding them out, and allow the functional test to focus on true functional faults. Leverage the power of boundary-scan to quickly generate tests for manufacturing faults and diagnose them accurately, significantly reducing the burden on functional test preparation and fault analysis.

Boundary-scan also brings substantial benefits to users of in-circuit test (ICT) systems, relieving them of constraints caused by the limitations of test fixtures. As board complexity increases, bed-of-nail access to BGAs and other types of packages becomes impractical or impossible. JTAG Technologies provides you with the next generation test solution, solving the access problems and reducing the number of test points required, either in a stand-alone test set-up, or integrated with one of our Symphony systems or with ICT vendors using JTAG Technologies products as integrated boundary-scan solutions.

| Test<br>Development<br>Packages | Netlist Com | Windows Gun | BSDL Checking | Test Compilet: | Test Execution | System-1 and 1 | Interactive T. | ATPG for Infra. | Infrastructure | Truth-Table p. | ATPG for Interior | ATPG for Mon | Test Pattern I. | Fault Course | Pin-Level Diagnostics |

|---------------------------------|-------------|-------------|---------------|----------------|----------------|----------------|----------------|-----------------|----------------|----------------|-------------------|--------------|-----------------|--------------|-----------------------|

| Basic                           | ~           | ~           | ~             | •              | ~              | •              | ~              | •               | ~              | •              |                   |              |                 |              | Opt.                  |

| Standard                        | ~           | ~           | ~             | ~              | ~              | ~              | ~              | •               | ~              | ~              | ~                 |              |                 |              | Opt.                  |

| Full                            | ~           | ~           | ~             | ~              | ~              | ~              | ~              | •               | ~              | ~              | ~                 | ~            | ~               |              | Opt.                  |

| Professional                    | v           | ~           | ~             | ~              | ~              | ~              | V              | ~               | V              | ~              | ~                 | ~            | ~               | ~            | Opt.                  |

# In-System **Programming Development**

In-system programming of flash memories and PLDs (CPLDs and FPGAs) is quick and easy using JTAG Technologies' development tools. Your applications can include any combination of programmable devices from multiple vendors, because of the broad range of supported devices, all covered by a uniform toolset.

#### Standard Flash Development Package

With our Standard Flash Development Package, you can configure flash devices on your board. The Standard Package

provides you with a convenient graphical user interface to design your application and to script the modules (such as ReadID, blank check, write and verify) you'll use later in production. If you have only a limited number of new designs, the Standard Package may be the solution for you.

#### Professional Flash Development Package

The Professional Package is ideal if you have several designs per year and need to respond rapidly to new projects.

With the Professional Package, your company maintains the flexibility to perform programming file generation as needed.

The Professional Package for flash features our advanced

Boundary-Scan Flash Programming Generator (BFPG). You'll quickly develop programming applications for new designs, using the extensive FlashLib library of the available devices, all generated automatically within our graphical user interface. FlashLib is updated regularly with the latest devices on the market, so your ability to automatically prepare flash application is continually assured.

#### Standard CPLD Development Package

The Standard CPLD Development Package is a fast, cost-effective development tool for reliable in-system

configuration of boundary-scan programmable logic devices. This package supports programming execution of all CPLDs that use JAM, STAPL, or IEEE 1532 insystem programming files. For other formats such as JEDEC, SVF and TTF, you will also need the Support Option(s) matching your CPLD family format(s). The Standard CPLD Development Package gives you full control over your board assuring that the board is in a predictable safe state while programming.

#### Professional CPLD Development Package

The Professional CPLD Development Package offers you all of the functionality as the Standard CPLD

Development package plus the advantage of automatic application generation with our unique BPPG - Boundary-scan PLD Programming Generator for IEEE 1532-compliant and non-compliant devices.

## CPLD Support Options

Support Options are used in combination with the Standard and Professional CPLD packages to develop appli-

cations for devices using JEDEC, SVF, or TTF programming formats. Support Options are not required for CPLD programming using JAM, STAPL or IEEE 1532 ISC formats.

With the CPLD Development packages, you avoid proliferation of dedicated programmers, one for each of the vendors, through the unified device support of the JTAG Technologies platform. This flexible, multi-vendor support is especially important in a manufacturing environment customarily confronted with multiple device sources needing to reduce the number of different programming tools.

| Programming<br>Development<br>Packages | Windows GUI | Netlist Converters<br>Test Utilitics | Compilation | Execution E. | AutoWrite S | Scripting | Automatic | Flash Library | IEEE 1532 E | JAM, S ABI PIT | Automated Irra | BPPG Autom | System-Level Support |

|----------------------------------------|-------------|--------------------------------------|-------------|--------------|-------------|-----------|-----------|---------------|-------------|----------------|----------------|------------|----------------------|

| Standard Flash                         | v .         | v v                                  | ~           | ~            | •           | •         |           |               |             |                |                |            | ~                    |

| Professional Flash                     | •           | v v                                  | ~           | ~            | ~           | ~         | ~         | ~             |             |                |                |            | ~                    |

| Standard CPLD                          | ~           | v v                                  | ~           | ~            |             |           |           |               | ~           | ~              |                |            | Opt.                 |

| Professional CPLD                      | ,           | v v                                  | ~           | V            |             |           |           |               | ~           | ~              | ~              | ~          | Opt.                 |

|                                        |             |                                      |             |              |             |           |           |               |             |                |                |            |                      |

## Boundary-Scan Technology

The IEEE 1149.1 standard defines a four-wire serial interface (a fifth wire is optional) designated the Test Access Port (TAP) to access complex integrated circuits (ICs) such as microprocessors, DSPs, ASICs, and CPLDs. In addition to the TAP, a compliant IC also contains shift registers and a state machine to execute the boundary-scan functions. Data entering the chip on the TDI (Test Data In) pin is stored in the instruction register or in one of the data registers. Serial data leaves the chip on the TDO (Test Data Out) pin. The boundary-scan logic is clocked by the signal on TCK (Test Clock), and the TMS (Test Mode Select) signal drives the state of the TAP controller. TRST\* (Test Reset) is optional and serves as a hardware reset signal.

Multiple scan-compatible ICs may be serially interconnected on the PCB, forming one or more boundary-scan chains, each chain having its own TAP. Each scan chain provides electrical access from the serial TAP interface to every pin on every IC that is part of the chain.

In normal operation, the IC performs its intended function as though the boundary-scan circuits were not present. However, when the device's scan logic is activated for the purpose of testing or in-system programming, data can be sent to the Internal

Core

Logic

TDI

Bypass

Instruction Reg.

ID Register

TCK

TRST\*

TAP Controller

IEEE 1149.1 Device Architecture

IC and read from it using the serial interface. This data may be used to stimulate the device core, drive signals outward from the device pins to the PCB, sense the input pins from the PCB and sense the device outputs. By providing access to the scan chain I/Os, the need for physical test points on the board is eliminated or greatly reduced, leading to significant savings as a result of simpler board layouts, less costly test fixtures, reduced time on in-circuit test systems, increased use of standard interfaces, and faster time-to-market.

In addition to board testing, boundary-scan allows programming almost all types of CPLDs and flash memories, regardless of size or package type, on the board, after PCB assembly. In-system programming saves money and improves throughput by reducing device handling, simplifying inventory management, and integrating the programming steps into the board production line.

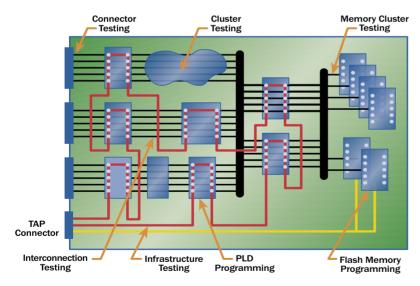

Applications of Boundary-Scan

Boundary-scan access can be extended beyond the board-level to create a unified system-level test strategy based on the IEEE 1149.1 architecture. JTAG Technologies development tools contain built-in support for a wide range of commercially available boundary-scan bridging and addressing devices. Recent industry efforts have advanced boundary-scan technology further, using IEEE 1149.1 as the basis for new standards for analog testing and measurement, high-speed digital testing, and uniform CPLD programming formats. As an active member of the standards development groups, JTAG Technologies is committed to delivering products that leverage the new capabilities of the evolving IEEE Standards.

# Test and In-System Programming **Production Systems**

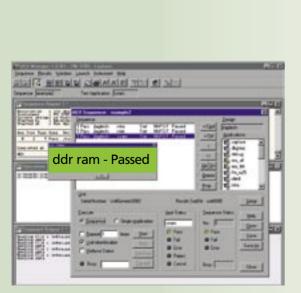

Applications created on any of the Test or Programming Development Packages run seamlessly in your production systems. A broad range of production environments are supported, from a stand-alone PC- or workstation-based process for test and programming, to full integration into your production line—an architecture in which boundary-scan operations take place within another process step, such as functional, in-circuit, or flying probe testing.

Among the benefits in the factory of boundary-scan are fast pin-level diagnostics, a flexible test strategy, high throughput, easy switchover between products, and reduced board handling. Your production personnel—and your process—also benefit from having quick and easy controls for manufacturing operations.

JTAG Technologies offers several production runtime packages from which you can choose:

- Stand-Alone Production Package

- Production Integration Packages

- Boundary-Scan Upgrade Packages for In-Circuit Testers or Flying Probe Testers

Our powerful diagnostics module is available for use with all of the above runtime packages as well as with the test development packages. Further, the optional JTAG Visualizer greatly facilitates the process of diagnosing and repairing defective boards by showing the faults graphically in the layout and the schematics up to the pins (pin-level-diagnostics).

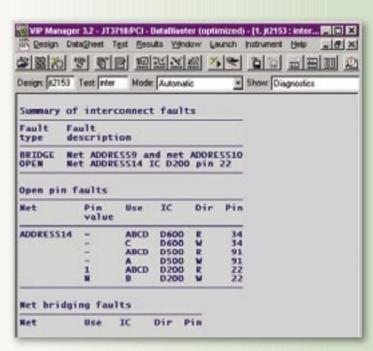

#### Advanced Intelligent Diagnostics for all Boundary-Scan Tests

JTAG Technologies advanced intelligent diagnostics lower your repair cycle times with accurate fault reporting even in cases of multiple faults on your board. Pin-level diagnostic

reporting applies to boundary-scan infrastructure testing, interconnections, memory and cluster tests. Diagnostics are run against the error file created during run-time, eliminating the need to re-run tests in repair and avoiding test correlation issues. And with a floating site license you can share the diagnostics module across multiple production lines. The end results are increased throughput and added value to your finished products.

**BSD Diagnostic Report**

| Production<br>Packages | Windows GIII | Command Line | Dynamic Link 1:: | Multiple Aut. | Link to Datahan | ICT/Flying Probe Integrass | Execution Control via Touristions | LabVIEW Drives | LabWindows (C.) | System-1 evol 6 | Script Creation | Pin-Level Diagnost. | SOLING |

|------------------------|--------------|--------------|------------------|---------------|-----------------|----------------------------|-----------------------------------|----------------|-----------------|-----------------|-----------------|---------------------|--------|

| Stand-Alone            | ~            | ~            |                  | ~             | •               |                            |                                   |                |                 | ~               | ~               | Opt.                |        |

| Production Integration |              | ~            | ~                |               |                 | Opt.                       | Opt.                              | Opt.           | Opt.            | ~               | Opt.            | Opt.                |        |

### **Production Software**

#### Stand-Alone Production Package

The Stand-Alone Production Package (PSA) provides all of the power of our test and programming systems,

with a minimum of architectural complexity, turning a PC into a complete boundary-scan test and programming station. After loading the appropriate applications from your development system, PSA's graphical application execution interface allows you to define the desired sequence of operations, including conditional branching and instructions to the operator. PSA is activated under three password-protected levels of control: for operators (test execution only), technicians (test flow modifications), and test engineers (test program changes).

Production personnel benefit from having quick and easy controls, along with execution reports summarizing the operations. Also, the Stand-Alone Package provides an easy way to report results formatted for your existing quality management system, such as TRACS (formerly from GenRad).

# Production Integration Packages

Perhaps you've already created an operator interface for other test and measurement applications. If so, one

of several Production Integration Packages will enable you to integrate boundary-scan test and programming within your existing factory process flow, thereby creating an operational sequence that includes boundary-scan along with other tests.

Each integration package contains an Application Program Interface (API) defining the communication between the integration package and the test executive. The boundary-scan applications are run in the form of sub-routines called from your test executive program. APIs are available for DLLs for programming in C/C++ and Visual Basic and for UNIX and Windows executables.

Furthermore, if you are currently using one of National Instruments' popular test programming environments, you'll find it a simple matter to integrate boundary-scan applications from JTAG Technologies into your test plan. For LabVIEW or LabWindows/CVI programming, the integration package APIs provide all of the instrument drivers and function panels that you will need to create your boundary-scan applications.

TestStand, National Instruments' powerful framework for building and customizing a full-featured test executive system, contains a set of predefined types of steps and allows the creation of custom types for specialized operations. The JTAG Technologies integration package for TestStand includes a set of custom JTAG step types dedicated specifically to performing boundary-scan testing and in-system programming.

GUI of Stand-Alone Production Package

**Production Integration Using JTAG Step Types for National Instruments' TestStand**

# Symphony<sup>™</sup> from JTAG Technologies **Boundary-Scan Upgrades for** In-Circuit Testers & Flying Probers

Combining boundary-scan testing and programming within an existing in-circuit tester, manufacturing

defect analyzer, or flying probe tester can result in a very efficient use of resources and a significant improvement in test coverage and flash/CPLD programming performance. Symphony from JTAG Technologies helps keep your capital expenditures to a minimum while the combination of boundary-scan with another structural test method allows you to achieve high testability even if your boards contain a mixture of digital and analog circuits. Other key benefits are reduced fixture test points made possible by boundary scan, simplified board handling in your production flow and the continued use of your familiar user interface, thereby reducing or eliminating the need for additional operator training.

The Symphony integration packages from JTAG Technologies boundary-scan upgrade paths for the following systems:

- Agilent 3070 (for all UNIX-based systems, regardless of the 3070 controller type in use, as well as for PC based 3070 systems)

- Teradyne 228x, TS12x, Spectrum and 1800 in-circuit testers

- Takaya APT-9400 flying probe test systems

These unique Symphony solutions deliver the benefits of both boundary-scan and ICT or FPT without disrupting your existing test methodology. Tests and in-system programming applications are generated on JTAG Technologies development tools and easily ported to the specific test system environment. In the case of integration with an ICT system, another major benefit is the reduction in fixture test points made possible by boundary-scan.

#### **JTAG Technologies Products in Third-Parties'** (OEM) Test Systems

In addition to the Symphony systems, a number of other test system integrations are available featuring JTAG Technologies boundary-scan products incorporated within popular third-party OEM testers. These solutions maximize test coverage by combining the strengths of test methods, and are available from Aeroflex (IFR), Digital Test, Scorpion, SEICA, SPEA and others. For more information, please contact the respective suppliers.

Integration with ICT and Flying Probe Systems

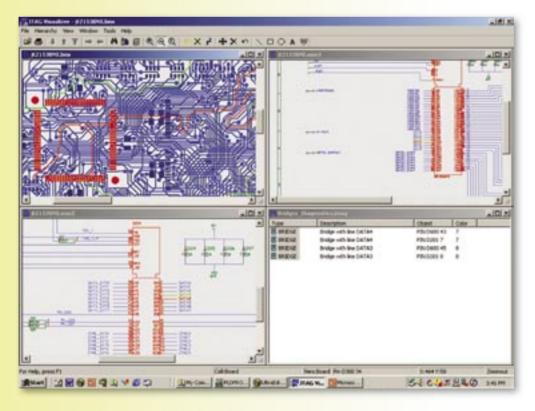

# Graphical Representation and Exploration JTAG Visualizer

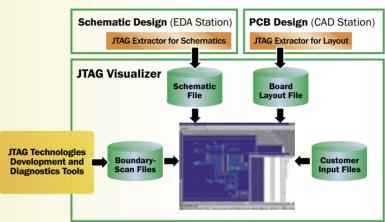

JTAG Visualizer is a powerful and unique tool to graphically view and explore boundary-scan results in your schematics and layouts, significantly enhancing your design-for-testability (DFT) results and streamlining the diagnostic/repair process. Used in conjunction with the Development and Production packages, JTAG Visualizer helps you quickly grasp boundary-scan data and results within your design for ease of comprehension and analysis. With its powerful search engine for finding and highlighting,

JTAG Visualizer greatly simplifies a variety of tasks such as identifying specific nets, components, or other items in the schematics or layouts.

JTAG Visualizer obtains the actual design files depicting the board schematic and layout by means of extractor modules loaded onto the EDA design environment. Boundary- scan information that is generated during test development, board repair or other activities is thus presented against the design data for unsurpassed accuracy and precision.

The browse, zoom and pan functions along with the unique coloring feature support intuitive navigation through design schematics and layout. For example, as a designer you may wish to check your schematics and/or layouts to assess boundary-scan design for testability (DFT). This function is provided by Visualizer by means of familiar graphical interactions and color representations. In manufacturing, JTAG Visualizer greatly facilitates diagnostics for repairing defective boards by showing the faults graphically in the layout and the schematics up to the pins (pin-level-diagnostics).

JTAG Visualizer Information Flow

JTAG Visualizer Display of Fault Appearance in PCB Schematic and Layout

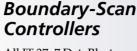

# Boundary-Scan Hardware

Whether you're using boundary-scan for test, in-system programming, or both, you have a broad choice of controllers and parallel I/O modules to drive your target system--all designed to meet production-level standards for reliability and ruggedness. Mission-readiness has been proven through literally thousands of installations world-wide.

JT 37x7/TSI

JT 3727/PXI

JT 3727/Compact PCI 6U

All JT 37x7 DataBlaster controllers share a common scalable architecture providing three performance classes and are available across a range of form factors. Choose the form factor and performance level that match your application and operating environment. Should needs change, it's a simple matter to increase the performance class with the addition of plug-in modules.

JT 37x7 controllers are available in the following form factors:

- Triple Serial Interface (TSI), with three interface types, Ethernet, USB 2.0 and 1.1, and FireWire all provided by a single compact unit

- PCI (other types of PC plug-in cards on request)

- PXI /CompactPCI format 3U

- CompactPCI format 6U

Furthermore, to meet industry requirements to maximize flash programming throughput in high volume production, the DataBlaster controllers support our unique Enhanced Throughput Technology $^{\text{TM}}$ .

Because of DataBlaster's sustained high clock speed (40 MHz), large on-board image memory, and data-compression techniques, this controller supports an exceptionally high data throughput.

As a result, flash programming, which requires a large number of scan operations, can be performed rapidly with DataBlaster, often at close to the inherent capability of the flash memory itself.

DataBlaster also provides other important throughput-accelerators:

- AutoWrite (patent pending)

which effectively reduces the

flash programming time by

a factor of two or three,

compared with conventional

boundary-scan methods

- Four-channel operation, allowing testing and flash memory programming to take place on up to four target boards in parallel (gang operation)

- Multiple controller operation for virtually unlimited throughput increase

In addition to the JT 37x7 series, we offer the IT 3710 controller in various formats, including PCI, PXI and VXI and the PM 3705 Explorer parallel port controller. JT 3710 is a four-channel, 25 MHz controller suitable for a wide variety of test and ISP applications. The Explorer boundary-scan controller operates on the parallel port PC interface, allowing it to be used in any desktop or laptop with a parallel port. Due to the modest speed of the parallel port, Explorer is best suited for test and PLD programming.

PM 3705/Explorer

# Parallel I/O Modules for Enhanced Test Access

High fault coverage makes a decisive difference in the cost and competitiveness of your product, because it translates directly into the throughput of your production process. Faults found with boundary-scan are diagnosed quickly, greatly easing the burden of functional testing.

Furthermore, improving the fault coverage will help shorten your time-to-market by assisting in prototype debug and board repair. JTAG Technologies provides a range of I/O modules to support testing of portions of the PCB that might otherwise be difficult to access with boundary-scan techniques.

Choose from the following products to achieve optimal and cost-effective test results:

- Desktop Digital I/O Scan (DIOS) modules with 64 channels

- DIMM-compliant DIOS cards with 133 I/O channels and programmable voltage levels for integration into your fixture

- DIMM carrier for maximum of two DIMM cards providing boundary-scan access to up to 256 customer-configurable test points

- PCI interface to simplify the testing of short and long-form PCI cards and to test the PCI slot in an equipment rack

Multiple DIOS cards and modules can be deployed to achieve a high quantity of additional test points accessible via boundary-scan.

#### High-Performance Signal Delivery

JT 37x7 and JT 3710 DataBlaster controllers are delivered with the QuadPOD system with active termination for maintaining excellent signal integrity and the highest possible performance at the target. The QuadPOD supports four detachable PODs for easy integration into your fixtures. Each POD is capable of driving a separate boundary-scan chain and each can be separately programmed for operating voltage from 1.3 V to 3.3 V (5 V tolerant.)

Depending on the test clock rate, QuadPOD can support extremely long distances to the target board. The detachable PODs are rated for industrial environments, allowing them to be located with the target(s) in system test chambers for environmental stress testing.

Besides QuadPOD, other signal delivery arrangements are available:

- Industrial TAP PODs for convenient signal termination within test fixtures

- TAP Extenders to lengthen the distance to the target and accommodate virtually any test setup

**Industrial POD**

Programmable DIMM DIOS

**Dual DIMM Carrier**

64-Bit PCI DIOS

64-Channel DIOS

PCI Slot

# Boundary-Scan Hardware

#### BSDL Generation and Verification Tool

Boundary-Scan Description Language (BSDL) files describe the IEEE 1149.1 logical implementation within a compliant IC and are vital to developing successful boundary-scan applications for testing and in-system programming. The BSDL Verifier from JTAG Technologies performs two important functions to help assure the availability of accurate BSDL files:

- To verify that an existing BSDL file accurately reflects the boundary-scan logic as actually implemented on an IC

- To generate a BSDL file, when one is not available, from the IC silicon itself

The BSDL Verifier is a valuable, low-cost tool for engineering departments of IC vendors, for ASIC design groups, and for test engineering departments to quickly prepare BSDL files and to verify their accuracy.

#### Analog Measurements Using IEEE 1149.4 Boundary-Scan

The JTAG 1149.4 Explorer allows you to explore and exploit the power of IEEE 1149.4 for implementing an analog boundary-scan architecture within analog or mixed-signal PCBs. This product contains all the hardware and software modules, general purpose analog instrumentation, and supporting documentation, to prepare and execute analog boundary-scan measurements on a Windows-based PC using a low-cost boundary-scan controller. The kit contains an evaluation board for your use and can also be applied to your own 1149.4-compliant target board.

#### High-Speed Digital Testing

For circuits compliant to the IEEE 1149.6 Standard for Boundary-Scan Testing of Advanced Digital Networks, high-speed serial links that are capacitively-coupled, differential, or a combination thereof, can be tested using JTAG Technologies tools.

**BSDL Creation and Verification Tool**

# Support and Services from JTAG Technologies

JTAG Technologies is committed to your success with boundary-scan. Boundary-scan is our sole, dedicated mission, and we firmly believe in the power of this technology. Our numerous customers with highly recognized names are strong evidence that we are meeting this vision. To assure that your enterprise receives all of the benefits of boundary-scan, we are prepared to provide the keys to help you exploit this technology throughout your product life cycles to maximize the return on your investments.

#### **Worldwide Support**

Our customer base includes many companies with a global presence and many others who operate locally. Regardless of the scope of your enterprise, we're prepared to support you with a worldwide professional team of field engineers throughout North America, Europe and Asia to assure you of the highest possible level of expertise. Support is available when you need it, where you need it, on-site or via phone or email, to assure rapid resolution of support questions.

#### **Getting Started**

To assist you in applying boundary-scan in the design phase, JTAG Technologies offers a thorough set of services and technical support at a level that is unmatched in the industry. You benefit by achieving the greatest possible testability and programmability for your designs while getting your engineering and operational personnel up to speed in the minimum time.

- Boundary-scan tutorials and seminars, in-person or via the Internet

- Training for developers, engineers and production personnel, including extensive hands-on sessions

- Testability reviews of your designs, prior to production

- In-system programmability reviews to maximize throughput

- Design and process consultation to optimize your test strategy

#### **Ongoing Support**

Once you've become familiar with the vast capabilities of boundary-scan, you'll want to secure your expertise level and take maximum advantage over the life of your products. Available support reflects the flexibility of production environments including a broad range of test system integrations.

- On-site support for stand-alone and integrated production systems

- Turn-key test development and programming file development

- Third-party Authorized Applications Providers

- Maintenance agreements for regular software updates and premium service

In line with our commitment to your success is helping you extend the value of your investments. Thus, it is our product policy to provide integration solutions for your existing test systems such as National Instruments products, Agilent and Teradyne in-circuit testers and Takaya flying probers. Also, other ATE vendors feature JTAG Technologies products within their systems.

# Unlocking the Power of Boundary-Scan

The potential benefits of JTAG Technologies' boundary-scan products to your operation are significant, with compelling savings in time and money.

#### ✓ Reduced time-to-market

Faster prototype debugging and faster production ramp-up. Engineers' factory-support effort is reduced.

#### ✓ Reduced capital investment

More efficient use of conventional ATE using much less expensive boundary-scan equipment, simplified fixtures, and system commonality for test and programming.

## ✓ Automated creation of test vectors and IC programming files

Speed the transition from design to factory with JTAG Technologies' advanced program generation products and integration with existing EDA tools.

#### √ Sound underlying product structure

Tools for development and manufacturing are based on an established standard, IEEE 1149.1, avoiding specialized ad-hoc methods.

#### ✓ Rapid resolution of manufacturing faults

Pin-level fault diagnosis is quick and easy with boundary-scan. Access problems are resolved even with surface-mount BGA and chip-scale packages.

## ✓ Elimination of inventory and handling of pre-programmed ICs

Fewer process steps, avoids damage to sensitive devices, improves reliability, supports just-in-time programming, eliminates IC sockets. No back-driving of IC avoiding potential damage to unit-under-test.

#### ✓ Commonality of method for test and programming throughout the product life cycle

Reduced learning time, improved inter-department process flow within R&D, production, and service.

JTAG Technologies and our authorized dealers are available worldwide to support your boundary-scan test and programming applications. For the latest in product information, useful application tips, and the name of the dealer nearest you, please contact us at one of the offices below or visit **www.jtag.com**.

#### USA, Canada and Mexico:

JTAG Technologies Inc. 1006 Butterworth Court Stevensville MD 21666 USA Phone: (Toll Free) 877 FOR JTAG Fax: 410 604 2109 Email: info@itag.com

#### Sweden:

JTAG Technologies Sweden Hollywoodvägen 1 SE-192 77 SOLLENTUNA Phone: +46 (0) 8 754 6200 Fax: +46 (0) 8 754 6200 Email: sweden@jtag.com

#### **United Kingdom:**

JTAG Technologies UK

Home Farm Business Centre

Cardington, MK44 3SN Bedford

Phone: +44 (0) 1234 831212

Fax: +44 (0) 1234 831616

Email: sales@jtag.co.uk

## China (also Malaysia, Singapore, Taiwan & Thailand):

JTAG Technologies China Baoan Tower #1205 800 Dong Fang Road, Pudang New District 200122 Shangai, China

Phone: +86 (021) 5831 1577 Fax: +86 (021) 5831 2167 Email: info@jtag.com.cn

#### Finland:

JTAG Technologies Finland PO Box 26 03101 Nummela Phone: +358 (0) 9 22431457 Fax: +358 (0) 9 22431467 Email: finland@jtag.com

#### **Europe and rest of the world:**

JTAG Technologies BV Headquarters Boschdijk 50 5612 AN Eindhoven, The Netherlands Phone: +31 (0) 40 2950870

Fax: +31 (0) 40 2950870 Fax: +31 (0) 40 2468471 Email: info@jtag.nl