## The Design of a **Central Processing** Unit

n this chapter, we will discuss the design of the controller for parts of a computer, called MODEL. MODEL has a word size of 32 bits. Instructions may require one or two words, depending on the addressing mode.

The format for the first word of a MODEL instruction is shown in Figure 10.1, where RN specifies the register number and AM specifies the address mode.

Figure 10.1 Instruction format for MODEL.

| 0 56 11 12 15 16      | 31 |

|-----------------------|----|

| Op-Code RN AM Address |    |

#### **DESCRIPTION OF MODEL** 10.1

In this section, we will specify the addressing modes and the instructions for which we will show the control sequence and discuss the timing. MODEL would surely have a wider variety of instructions and more addressing modes. However, those that we specify will be adequate to demonstrate the process of design.

#### **Memory and Register Set** 10.1.1

MODEL has a memory space of  $2^{32}$  words,\* each 32 bits wide. To access memory, the address is placed on lines AD [0:31] for one clock period. For read, a 1 is placed on line **read** at that same time, and the contents

\*This implies a 32-bit address and a maximum memory of 2<sup>32</sup> words. Not all of the memory needs to be there for the system to work properly.

FIRST PA

of that memory location will be available on bus DATA [0:31] during that clock period. Thus, a typical memory fetch step might be AD = PC; read = 1; IR  $\leftarrow$  DATA. To store in memory, the word is connected to DATA (at the same time as the address is on AD) and a 1 is put on line write, for example AD = PC; DATA = WORK; write = 1. We will examine the modifications needed to handle a slower memory in Section 10.4. DATA is an INTERSYSTEM BUS. ADIN, read, and write could be thought of as OUTPUT LINES from MODEL or as an INTERSYS-TEM BUS. We will treat them as the latter; they are part of BUS, as shown in Figure 8.1. The register set of MODEL includes the following registers: PC[0:31] The program counter IR[0:31]<sup>§</sup> The instruction register-a place to store the first word of an instruction while it is being decoded and executed REG[0:63; 0:31]\* A set of 64 general-purpose registers WORK[0:31]<sup>§</sup> A register to hold data temporarily EA[0:31]<sup>§</sup> Register in which the effective address is computed Zero flag bit—set to 1 when the result of 7. some instructions is  $zero^{\dagger}$  (0 otherwise) Negative flag bit-set to 1 when the n result of some instructions is negative (leading bit is 1) Carry (and borrow) bit-stores the carry C out of the most significant bit of the adder Two's complement overflow bit-set to τ/ 1 if the result of an operation is out of range, assuming operands are in two's complement notation (0 otherwise) Registers indicated with a § contain no useful information between

2

3

45

6

7

8 9

1

2

3

4

5

6

7

8

0

20

1

2

3

4

5

6

7

8

9

30

1

2

3

4

5

6 7

8

9

40 1 2

3

4

5

Registers indicated with a § contain no useful information between instructions. If we expand the instruction set, we may need to add some registers.

<sup>\*</sup>REG<sup>3F</sup> will be used as the stack pointer; we will use the notation SP in the DDL, but will define it as REG<sup>3F</sup> with a NAME definition line.

<sup>&</sup>lt;sup>†</sup>When we describe the instructions in Section 10.1.2, we will specify which instructions modify which flag bits.

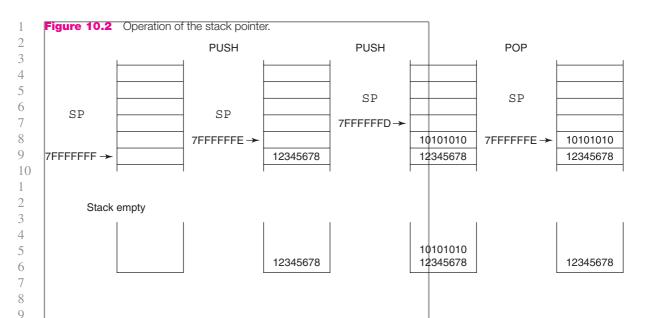

The stack in MODEL is stored in memory. The register SP points to 20 the next empty place on the stack. Elements are stored in descending order on the stack. Thus, if the stack pointer contains 7FFFFFFF and something is pushed onto the stack, it is stored in location 7FFFFFFF and the stack pointer is then decremented to 7FFFFFFE. Figure 10.2 shows the behavior of the stack with two items being pushed onto the stack and then one popped from the stack. Note that the SP is decremented on pushes and incremented on pops. When something is popped, it is not erased; it is copied to the Central Processing Unit (CPU) and the pointer is incremented. After the pop, the contents of 7FFFFFE are still there but will never be used by a stack instruction. A push would write over it; a 30 pop would first increment SP and take the contents of 7FFFFFF.

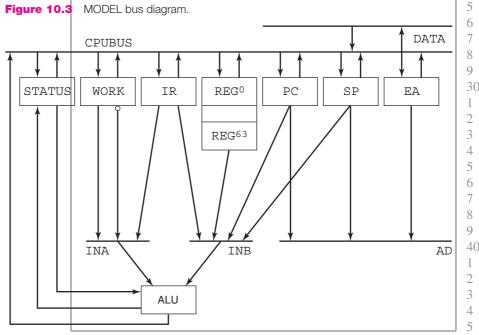

Internally, data is transferred by way of a 32-bit internal bus, CPUBUS. In addition, the arithmetic and logic unit has two 32-bit input buses: INA and INB. In describing the behavior of the machine, these buses are not referenced most of the time. A statement

REG/IR<sub>6:11</sub> ← WORK.

1

2

3

4

5

6

7

8

9

1

2

3

4

5 6

7

8

9 40

1 2

3 4

5

implies that WORK is connected to CPUBUS and the data on that bus is clocked into the register, that is,

CPUBUS = WORK; REG/IR<sub>6:11</sub>  $\leftarrow$  CPUBUS.

WORK  $\leftarrow$  ADD<sub>1:32</sub> [FFFFFFF; WORK; 0]

implies the constant FFFFFFFF is connected to one 32-bit input of the adder. WORK is connected to the other 32-bit input. 0 is connected to the

EXAMPLE 10.1

**C**<sub>in</sub> input, the right 32 bits of the adder output is connected to CPUBUS, 1 and the bus is clocked into WORK. In this example, the carry output of the 2 3 adder is not stored anywhere,

4

5

6 7

8

3

4

INA = FFFFFFF; INB = WORK; **c**<sub>in</sub> = 0; BUS = ADD<sub>1:32</sub> [INA; INB; **c**<sub>in</sub>]; WORK ← CPUBUS

If we wanted to store that in the **c** flip flop, we would have written

c, WORK ← ADD[FFFFFFF; WORK; 0]

Since there is no other way to move data, it is not necessary to be more specific.

Figure 10.3 shows a simplified block diagram of the bus structure. 4 5 The constants, partial register connections, and shifted WORK are not shown, (For example, WORK  $\leftarrow$  FFFF, IR<sub>16:31</sub> implies the constant 6 FFFF is connected to the left half of CPUBUS and only the right half of 7 8 IR is connected to the right half of CPUBUS.)

In addition to the three internal busses, there are two intersystem 9 busses: DATA and AD. (The bus signals read and write are not 20 shown.) Note that INA, INB, AD, **read** and **write** are really only 1 2 multiplexors, with data only going in one direction. (However, in a larger 3

system where memory is used by more than one subsystem, AD, **read**, and write may be buses.)

### 10.1.2 Addressing Modes

We will define 7 addressing modes (of the 16 possibilities with 4 bits), treating the remaining 9 as no-ops (no operation). Some of the Examples, Solved Problems, and Exercises will suggest others. In each of the following examples, we will show what happens for a load register instruction (LOD), where RN is assumed to be 5 (05). The first four modes require a one-word instruction; the others require a second word. The AM field is shown in binary, rather than hexadecimal, to simplify the discussion later.

**Register (AM = 0000)** The data comes from or is stored in the one of the 64 registers specified by  $IR_{26:31}$ .\* This mode is not valid for branch instructions, since they require a memory address.

*Example:* LOD REG<sup>5</sup>, REG<sup>14</sup>  $[IR_{26:31} = OE]$ The data in Register 14 is loaded into Register 5.

**Register indirect (AM = 0010)** The register specified by  $IR_{26:31}$  contains the address in main memory of the data or where the result is to be stored or the jump is to go.

*Example*: LOD REG<sup>5</sup>, (REG<sup>14</sup>)  $[IR_{26:31} = OE]$ where REG<sup>14</sup>: 12345678 The data in memory location 12345678 is loaded into Register 5.

**Page zero (AM = 0110)** Bits  $IR_{16:31}$  are zero-extended to produce the effective address.

*Example*: LOD REG<sup>5</sup>, z1234  $[IR_{16:31} = 1234]$ The data in memory location 00001234 is loaded into Register 5.

**Relative (AM = 0111)** Bits  $IR_{16:31}$  are sign-extended and added to the program counter (after the program counter has been incremented to point to the next instruction) to produce the effective address.

*Example*: LOD REG<sup>5</sup>, @1234 [IR<sub>16:31</sub> = 1234] If this instruction is at address 01120111, the effective address is

00001234 + 01120111 + 1 = 01121346.

The data in memory location 01121346 is loaded into Register 5.

\*In those modes where the address field specifies a register, IR<sub>16:25</sub> (the rest of the address field) are ignored.

|              | <i>Example</i> : LOD REG <sup>5</sup> , @8000 $[IR_{16:31} = 8000]$<br>If this instruction is at address 01120111, the effective address is                                                                                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | FFFF8000 + 01120111 + 1 = 01118112.                                                                                                                                                                                                                                                                       |

|              | The data in memory location 01118112 is loaded into Register 5.                                                                                                                                                                                                                                           |

|              | <b>Direct (AM = 1000) [IR<sub>16:31</sub> are ignored]</b> A second word of the instruction is required. That word contains the effective address.                                                                                                                                                        |

|              | <i>Example</i> : LOD REG <sup>5</sup> , 12345678<br>The contents of memory location 12345678 is loaded into Register 5.                                                                                                                                                                                   |

|              | <b>Indirect (AM = 1001)</b> [IR <sub>16:31</sub> are ignored] A second word of the instruction is required. It contains the address in memory where the effective address of data is found.                                                                                                               |

|              | <i>Example</i> : LOD REG <sup>5</sup> , (12345678)                                                                                                                                                                                                                                                        |

|              | M[12345678] = 56789ABC                                                                                                                                                                                                                                                                                    |

|              | The contents of 12345678 are fetched. Then the contents of memory location 56789ABC are loaded into Register 5.                                                                                                                                                                                           |

|              | <b>Immediate (AM = 1100)</b> [IR <sub>16:31</sub> are ignored] A second word of the instruction is required. It contains the data. This type is not valid for any instruction that requires an address (for storing a result or branching).                                                               |

|              | <i>Example:</i> LOD REG <sup>5</sup> , #12345678<br>The number 12345678 is loaded into Register 5. (The constant 12345678 is contained in the second word of the instruction.)                                                                                                                            |

| EXAMPLE 10.2 | We have an instruction to ADD the number specified by the addressing to REG <sup>4</sup> , where                                                                                                                                                                                                          |

|              | This instruction is at location 12341234<br>The second word of the instruction (if any) is 20000000<br>Bits 16 to 31 of this instruction word are AB07<br>$REG^4 = 00000102$<br>$REG^7 = 00123344$<br>M[0000AB07] = 11111111<br>M[00123344] = FFFFFFE<br>M[1233BD3C] = 44332211<br>M[20000000] = 00123344 |

|              | We will examine which registers (not including the flag bits) are changed for each addressing type.                                                                                                                                                                                                       |

|              | Register $REG^4 \leftarrow 00123446$ (00000102 + 00123344)                                                                                                                                                                                                                                                |

### 540

| 1  |   |

|----|---|

| 2  |   |

| 3  |   |

| 4  |   |

| 5  |   |

| 6  |   |

| 7  |   |

| 8  |   |

| 9  |   |

| 1  |   |

| 1  | 0 |

| 2  |   |

| 3  |   |

| 4  |   |

| 45 |   |

|    |   |

| 6  |   |

| 7  |   |

| 8  |   |

| 9  |   |

| 2  | 0 |

| 1  |   |

| 2  |   |

| 3  |   |

| 4  |   |

| 5  |   |

| 6  |   |

| 7  |   |

| 8  |   |

| 9  |   |

| 3  | 0 |

| 1  |   |

| 2  |   |

| 3  |   |

| 4  |   |

| 5  |   |

| 6  |   |

| 7  |   |

| 8  |   |

| 9  |   |

| 4  | 0 |

| 1  |   |

| 2  |   |

| 3  |   |

| 4  |   |

| 5  |   |

| Register indirect | REG <sup>4</sup> ← 00000100 | (00000102 + FFFFFFE)  |

|-------------------|-----------------------------|-----------------------|

|                   | PC ← 12341235               |                       |

| Page zero         | REG <sup>4</sup> ← 11111213 | (00000102 + 11111111) |

|                   | PC ← 12341235               |                       |

| Relative          | Address = 12341234          | + 1 + FFFFAB07 =      |

|                   | 1233BD3C                    |                       |

|                   | REG <sup>4</sup> ← 44332313 | (00000102 + 44332211) |

|                   | PC ← 12341235               |                       |

| Direct            | REG <sup>4</sup> ← 00123446 | (00000102 + 00123344) |

|                   | PC ← 12341236               |                       |

| Indirect          | REG <sup>4</sup> ← 00000100 | (00000102 + FFFFFFE)  |

|                   | PC ← 12341236               |                       |

| Immediate         | REG <sup>4</sup> ← 20000102 | (00000102 + 20000000) |

|                   | PC ← 12341236               |                       |

[SP 1, 2; EX 1]

## 10.1.3 Instruction Set of MODEL

In this section, we will define a subset of the instructions, enough to illustrate the design of the controller. For each, we will specify a threeletter mnemonic and the flag bits that are affected. We will not assign an op-code; rather, we will implement the controller, assuming that an appropriate decoder is included. However, those instructions that do not use the address portion (for example, Return from subroutine) begin with a 1; others begin with a 0. For each of the examples, we will assume that we used direct addressing and that

The effective address is 12345678 M[12345678] = 10101234 REG<sup>3</sup> = FFFFFF8 SP = 7FFFFF6 M[7FFFFF7] = 98765432

### Data Movement\*

LOD z n Load register with data specified by the address field<sup>†</sup>

Example: LOD REG<sup>3</sup>, 12345678

$\operatorname{REG}^3 \leftarrow 10101234 \quad z \leftarrow 0 \quad n \leftarrow 0$

STO Store register in location specified by the address field (either memory or a register)

\*We will use REG<sup>63</sup> for the stack pointer and thus will not need special instructions to load or store SP.

register addressing.

<sup>&</sup>lt;sup>\*</sup>Either the contents of the memory location specified by EA, or the data for immediate or

| Example:     | STO REG <sup>3</sup> , 12345678                                                                                                                                          | $\begin{bmatrix} 1 \\ 2 \end{bmatrix}$ |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

| M[1          | 2345678] ← FFFFFF8                                                                                                                                                       | $\begin{vmatrix} 2\\ 3 \end{vmatrix}$  |

| PSH          | Push register onto the stack                                                                                                                                             | 4                                      |

| Example:     | PSH REG <sup>3</sup>                                                                                                                                                     | 5                                      |

| M[7          | FFFFFF6] ← FFFFFF8 SP ← 7FFFFFF5                                                                                                                                         | 7                                      |

| PSH and F    | POP use only a register; the address field is ignored.                                                                                                                   | 8                                      |

| POP z n      | Pop top of stack to register                                                                                                                                             | 9                                      |

| Example:     | POP REG <sup>3</sup>                                                                                                                                                     | 1                                      |

| SP ←         | $-7FFFFF7 \operatorname{REG}^3 \leftarrow 98765432  z \leftarrow 0  n \leftarrow 1$                                                                                      | 23                                     |

| Arithmetic I | Instructions                                                                                                                                                             | 4                                      |

| ADD z n      | <i>c v</i> Add number specified by the address field to the register                                                                                                     | 5<br>6<br>7                            |

| Example:     | ADD REG <sup>3</sup> , 12345678                                                                                                                                          | 8                                      |

|              | FFFFFF8                                                                                                                                                                  | 9                                      |

| (1)          | $\frac{10101234}{1010122C}$                                                                                                                                              | $\begin{vmatrix} 2\\ 1 \end{vmatrix}$  |

| (1)<br>REC   | $3^3 \leftarrow 1010122C$ $z \leftarrow 0$ $n \leftarrow 0$ $c \leftarrow 1$ $v \leftarrow 0$                                                                            | 2                                      |

|              |                                                                                                                                                                          | 3<br>4                                 |

| ADC z n      | <i>c v</i> Add with carry; add number specified by the address field to the register and the <i>c</i> flag                                                               | 5                                      |

| Example:     | ADC $\text{REG}^3$ , 12345678 ( <i>c</i> was 1)                                                                                                                          | 7                                      |

| REC          | $G^3 \leftarrow 1010122D  z \leftarrow 0  n \leftarrow 0  c \leftarrow 1  v \leftarrow 0$                                                                                | 8                                      |

| Example:     | ADC REG <sup>3</sup> , 12345678 ( <i>c</i> was 0)                                                                                                                        | 3                                      |

| REC          | $G^3 \leftarrow 1010122C$ $z \leftarrow 0$ $n \leftarrow 0$ $c \leftarrow 1$ $v \leftarrow 0$                                                                            | $\begin{vmatrix} 1\\ 2 \end{vmatrix}$  |

| SUB z n      | <i>c v</i> Subtract number specified by the address field from the register                                                                                              | 3<br>4                                 |

| Example:     | SUB REG <sup>3</sup> , 12345678                                                                                                                                          | 5<br>6                                 |

|              | 1                                                                                                                                                                        | 0                                      |

|              | FFFFFF8                                                                                                                                                                  | 8                                      |

|              | EFEFEDCB                                                                                                                                                                 | 9                                      |

| (1)          | EFEFEDC4                                                                                                                                                                 | 1                                      |

| REC          | $G^3 \leftarrow \text{EFEFEDC4}  z \leftarrow 0  n \leftarrow 1  c \leftarrow 1  v \leftarrow 0$                                                                         |                                        |

| CMP z n      | <i>c v</i> Compare; behaves the same as subtract, but does not store the difference back to the register. (It is used to compare the same number with several words from | 2<br>3<br>4<br>5                       |

|              | memory without having to reload the register.)                                                                                                                           |                                        |

## SI Ex

| Engineela                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Example:                                                                               | CMP REG <sup>3</sup> , 12345678                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $z \leftarrow$                                                                         | $0  n \leftarrow 1  c \leftarrow 1  v \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| INC z n                                                                                | Increments number specified by the address; ignores RN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Example:                                                                               | INC 12345678                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| M[12                                                                                   | $2345678] \leftarrow 10101235  z \leftarrow 0  n \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| gic, Shift,                                                                            | and Rotate Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| NOT z                                                                                  | Bit-by-bit complement; ignores RN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Example:                                                                               | NOT 12345678                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| M[12                                                                                   | $2345678] \leftarrow \text{EFEFEDCB}  z \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| AND <i>z n</i>                                                                         | Bit-by-bit AND of register with number specified by the address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Example:                                                                               | AND REG <sup>3</sup> , 12345678                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                        | 1111 1111 1111 1111 1111 1111 1111 1000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AND                                                                                    | 0001 0000 0001 0000 0001 0010 0011 0100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                        | 0001 0000 0001 0000 0001 0010 0011 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| REG                                                                                    | $^{3} \leftarrow 1010230  z \leftarrow 0  n \leftarrow 0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| ASR z                                                                                  | Arithmetic shift right of number specified by the address; number of places specified by the right 5 bits of RN ( $IR_{7:11}$ )*                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                                                                                        | address; number of places specified by the right 5 bits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| ASR z<br>Example:                                                                      | address; number of places specified by the right 5 bits of RN $(IR_{7:11})^*$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ASR z<br>Example:                                                                      | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ASR z<br>Example:<br>M[12                                                              | <ul> <li>address; number of places specified by the right 5 bits of RN (IR<sub>7:11</sub>)*</li> <li>ASR 3, 12345678</li> <li>2345678] ← 02020246 z ← 0</li> <li>Rotate right number specified by the address; number</li> </ul>                                                                                                                                                                                                                                                                                                                                        |

| ASR z<br>Example:<br>M[12<br>ROR<br>Example:                                           | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678<br>2345678] $\leftarrow$ 02020246 $z \leftarrow 0$<br>Rotate right number specified by the address; number<br>of places specified by the right 5 bits of RN                                                                                                                                                                                                                                                                                                  |

| ASR z<br>Example:<br>M[12<br>ROR<br>Example:<br>M[12                                   | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678<br>2345678] ← 02020246 z ← 0<br>Rotate right number specified by the address; number<br>of places specified by the right 5 bits of RN<br>ROR 3, 12345678<br>2345678] ← 82020246                                                                                                                                                                                                                                                                              |

| ASR z<br>Example:<br>M[12<br>ROR<br>Example:                                           | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678<br>2345678] ← 02020246 z ← 0<br>Rotate right number specified by the address; number<br>of places specified by the right 5 bits of RN<br>ROR 3, 12345678<br>2345678] ← 82020246                                                                                                                                                                                                                                                                              |

| ASR z<br>Example:<br>M[12<br>ROR<br>Example:<br>M[12<br>anch Instr                     | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678<br>2345678] ← 02020246 z ← 0<br>Rotate right number specified by the address; number<br>of places specified by the right 5 bits of RN<br>ROR 3, 12345678<br>2345678] ← 82020246<br><b>uctions</b><br>Jump to the address if the condition specified by the right<br>4 bits of RN (IR <sub>8:11</sub> ) is met; otherwise, continue to the next                                                                                                               |

| ASR z<br>Example:<br>M[12<br>ROR<br>Example:<br>M[12<br>anch Instr<br>JMP <sup>†</sup> | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678<br>2345678] ← 02020246 z ← 0<br>Rotate right number specified by the address; number<br>of places specified by the right 5 bits of RN<br>ROR 3, 12345678<br>2345678] ← 82020246<br><b>uctions</b><br>Jump to the address if the condition specified by the right<br>4 bits of RN (IR <sub>8:11</sub> ) is met; otherwise, continue to the next<br>step. Branch conditions are specified in Table 10.1.                                                       |

| ASR z<br>Example:<br>M[12<br>ROR<br>Example:<br>M[12<br>anch Instr                     | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678<br>2345678] ← 02020246 z ← 0<br>Rotate right number specified by the address; number<br>of places specified by the right 5 bits of RN<br>ROR 3, 12345678<br>2345678] ← 82020246<br><b>uctions</b><br>Jump to the address if the condition specified by the right<br>4 bits of RN (IR <sub>8:11</sub> ) is met; otherwise, continue to the next<br>step. Branch conditions are specified in Table 10.1.<br>Call subroutine, save return address on the stack. |

| ASR z<br>Example:<br>M[12<br>ROR<br>Example:<br>M[12<br>anch Instr<br>JMP <sup>†</sup> | address; number of places specified by the right 5 bits<br>of RN (IR <sub>7:11</sub> )*<br>ASR 3, 12345678<br>2345678] ← 02020246 z ← 0<br>Rotate right number specified by the address; number<br>of places specified by the right 5 bits of RN<br>ROR 3, 12345678<br>2345678] ← 82020246<br><b>uctions</b><br>Jump to the address if the condition specified by the right<br>4 bits of RN (IR <sub>8:11</sub> ) is met; otherwise, continue to the next<br>step. Branch conditions are specified in Table 10.1.                                                       |

5 reference.

<sup>&</sup>lt;sup> $\hat{T}$ </sup> For conditional Jumps and Calls, the condition is specified by a hexadecimal digit, such as JM2 for Jump if *n* is 1 or CL7 for Call if v = 0.

|              |                                                       | Table 1                                                  | 0.1 Branch c                                                                    | onditions.                   |                                                                                                                                    |          |

|--------------|-------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|----------|

|              |                                                       | <i>RN</i> <sub>8:11</sub>                                | Condition                                                                       | <i>RN</i> <sub>8:11</sub>    | Condition                                                                                                                          |          |

|              |                                                       | 0000<br>0001<br>0010<br>0011                             | z<br>z'<br>n<br>n'                                                              | 1000<br>1001<br>1010<br>1011 | not used<br>not used<br>not used<br>not used                                                                                       |          |

|              |                                                       | 0100<br>0101<br>0110<br>0111                             | с<br>с'<br>v<br>v'                                                              | 1100<br>1101<br>1110<br>1111 | not used<br>not used<br>not used<br>always                                                                                         |          |

| EXAMPLE 10.3 |                                                       | ok at instr                                              | uctions refere                                                                  | ncina roaista                | er 4 (REG <sup>4</sup> ), using Pag                                                                                                | ae zero  |

|              | addressing                                            |                                                          |                                                                                 | nong registe                 | $r + (n \cup G), using Pa($                                                                                                        | ye zero  |

|              | PC =<br>REG <sup>4</sup><br>REG <sup>6</sup><br>M[000 | 1234123<br>= 00000<br><sup>3</sup> (SP) = 7<br>00AB07] = | 102                                                                             | n word are /                 | 4B07                                                                                                                               |          |

|              |                                                       | uction typ                                               | -                                                                               |                              | y locations are chang<br>ise, the PC is increme                                                                                    | ented to |

|              | LOD<br>STO<br>PSH<br>POP                              | M[00<br>M[7F<br>REG <sup>6</sup>                         | <sup>63</sup> (SP) ← 7FFF                                                       | 0000102<br>0000102 R         | ← 1<br>EG <sup>63</sup> (SP) ← 7FFFFF4<br>4 <sup>4</sup> ← 00000000                                                                |          |

|              | ADD<br>ADC                                            | REG <sup>∠</sup><br>For <i>c</i>                         | = 0, same as                                                                    | ADD, for c                   | $\begin{array}{c} \leftarrow 1  c \leftarrow 0  v \leftarrow 0 \\ = 1 \\ \leftarrow 1  c \leftarrow 0  v \leftarrow 0 \end{array}$ |          |

|              | SUB<br>CMP<br>INC                                     | Z ← (                                                    | <sup>I</sup> ← 7EEEFF1<br>) <i>n ←</i> 0 <i>c</i> <<br>00AB07] ← 8 <sup>-</sup> | ÷0 v ← 0                     | $\leftarrow 0  c \leftarrow 0  v \leftarrow 0$ $\leftarrow 0  n \leftarrow 1$                                                      | )        |

|              | NOT<br>AND<br>ASR                                     | REG                                                      | 00AB07] ← 7E<br><sup>I</sup> ← 00000100<br>00AB07] ← F8                         | ) z ← 0 n                    |                                                                                                                                    |          |

|              | ROR<br>JMP<br>CLL                                     | M[00<br>PC ←<br>PC ←                                     | 00AB07] ← 18<br>- 0000AB07                                                      | 8111111<br>M[7FFFFF          | 5] ← 12341235                                                                                                                      |          |

|              | RTS                                                   |                                                          | $(SP) \leftarrow 7FFF$<br><sup>53</sup> (SP) $\leftarrow 7FFF$                  |                              | ← 00000000                                                                                                                         |          |

[SP 3, 4; EX 2, 3]

### 544

## **10.2** CONTROL SEQUENCE FOR MODEL\*

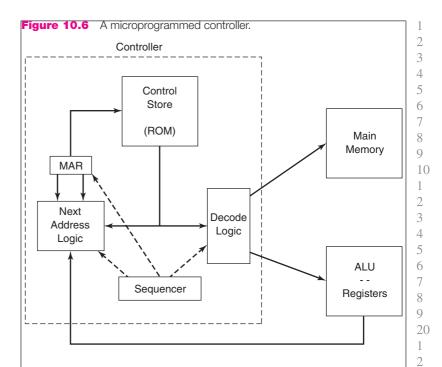

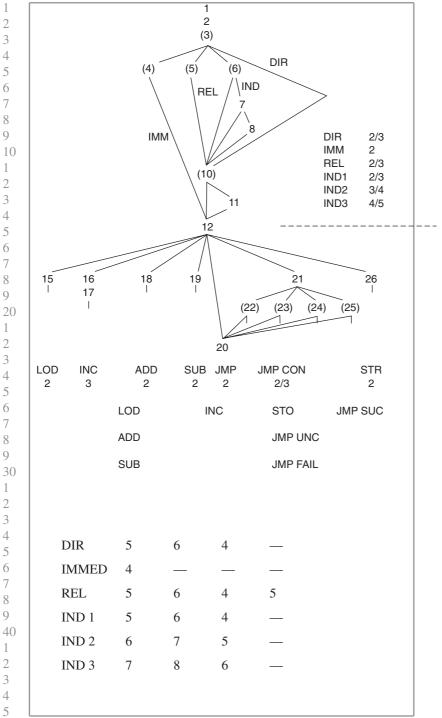

In this section, we will develop a straightforward control sequence to implement that part of MODEL described in the previous two sections. In the next sections, we will look at its implementation with a hard-wired controller and a microprogrammed controller.

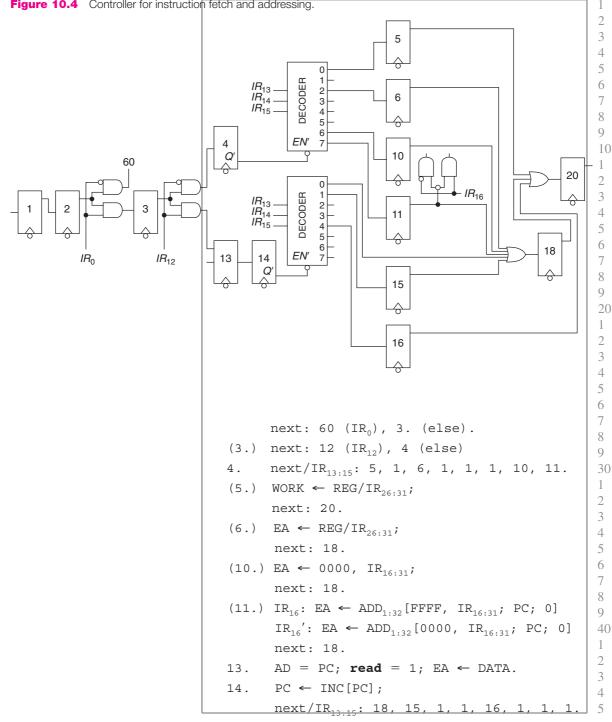

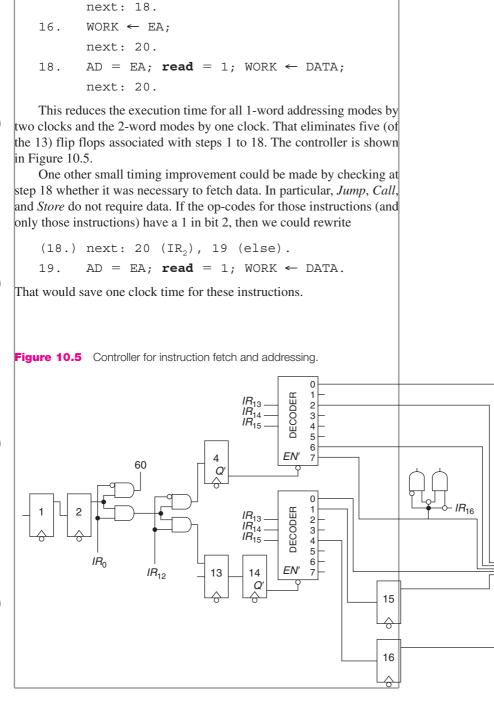

The first word of an instruction is read into the Instruction Register (IR) in the first step of the control sequence. Next, at step 2, the program counter is incremented to point to the next word (either the second word of this instruction or, if this is a one-word instruction, the first word of the next instruction). Throughout the design of the sequencer, we will use INC to represent an incrementer and DEC to represent a decrementer. In practice, there may be such a device as part of the ALU, or these may be implemented using the adder, putting a 1 or -1 on one of the inputs. Also, at step 2, we branch to step 60, the instruction decode step for those instructions where no address is required, or continue to step 3 for address computation.

AD = PC; read = 1; IR ← DATA.

PC ← INC[PC]; next: 60 (IR₀), 3. (else).

The addressing mode of all one-word instructions begins with a 0, and that for two-word instructions begins with a 1. At step 3, we separate these.

3. next: 12 (IR<sub>12</sub>), 4 (else)

4. next/IR<sub>13:15</sub>: 5, 1, 6, 1, 1, 1, 10, 11.

Unused codes are treated as no-ops, branching back to step 1 to fetch a new instruction. When addressing is completed, the address (if there is one) is stored in EA; control then goes to step 18 to fetch data. Those addressing modes that produce data, but no address (immediate and register), store that data in WORK and branch to step 20.

For register and register indirect addressing, bits 26 to 31 specify the register. Thus, at step 5, that register is moved to WORK (for register addressing), and control goes next to step 20. At steps 6 (for register indirect), that register is moved to EA, with control going to step 18.

### Register

5. WORK  $\leftarrow$  REG/IR<sub>26:31</sub>; next: 20.

### **Register Indirect**

6. EA ← REG/IR<sub>26:31</sub>;

next: 18.

\*A complete listing of the control sequence for a hard-wired controller implementation of MODEL is found in Appendix A. To follow the design from this section, ignore the

parentheses around step numbers in the appendix.

For Page zero addressing, the address field  $(IR_{16:31})$  is zero-extended (that is, leading 0's are added to make the number 32 bits). For relative addressing, the sign-extended address field is added to the program counter (which had already been incremented to point to the next instruction at step 2). Both produce an address and thus branch to step 18.

#### Page Zero

10. EA ← 0000, IR<sub>16:31</sub>;

next: 18.

#### Relative

11.  $IR_{16}$ : EA  $\leftarrow ADD_{1:32}$  [FFFF,  $IR_{16:31}$ ; PC; 0]  $IR_{16}'$ : EA  $\leftarrow ADD_{1:32}$  [0000,  $IR_{16:31}$ ; PC; 0] next: 18.

The remaining three address modes all require a second word. At steps 13 and 14, the second word of the instruction is read into EA, and the program counter is incremented. For direct addressing, the second word is the effective address and is sent to EA. For indirect addressing, the second word is the address where the effective address will be found. Thus, after the second word is read at step 13, that memory location is read (step 15) and its contents are sent to EA.

### **Read Second Word, Direct**

```

13. AD = PC; read = 1; EA ← DATA.

14. PC ← INC[PC];

next/IR<sub>13:15</sub>: 18, 15, 1, 1, 16, 1, 1, 1.

```

#### Indirect

15. AD = EA; read = 1; EA ← DATA; next: 18.

For immediate addressing, the second word is the data and is sent to WORK, and control branches to step 20 (since a read is not needed for data).

#### Immediate

16. WORK ← EA; next: 20.

At step 18, we read the data from the effective address register, EA, into WORK. We could have a branch to skip this step for those instructions that do not require data (such as store, jump, and call).

#### Data Read

18. AD = EA; read = 1; WORK ← DATA; next: 20.

45

| We want to add two new addressing modes; register indirect with auto-post-<br>incrementing, and short immediate. Assume that step 4 branches to steps 7<br>and 9 for these. Register indirect with auto-post-incrementing produces the<br>same address as register indirect, but also increments the register after using<br>it. For short immediate, the address field is sign-extended. | EXAMPLE 10.4 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| Register Indirect with Auto-Post-Incrementing                                                                                                                                                                                                                                                                                                                                             |              |

| 7. EA $\leftarrow$ REG/IR <sub>26:31</sub> .                                                                                                                                                                                                                                                                                                                                              |              |

| 8. REG/IR <sub>26:31</sub> ← INC[REG/IR <sub>26:31</sub> ];                                                                                                                                                                                                                                                                                                                               |              |

| next: 18.                                                                                                                                                                                                                                                                                                                                                                                 |              |

| Short Immediate                                                                                                                                                                                                                                                                                                                                                                           |              |

| 9. $IR_{16}$ : WORK $\leftarrow$ FFFF, $IR_{16:31}$ ;                                                                                                                                                                                                                                                                                                                                     |              |

| IR <sub>16</sub> ': WORK ← 0000, IR <sub>16:31</sub> ;                                                                                                                                                                                                                                                                                                                                    |              |

| next: 20.                                                                                                                                                                                                                                                                                                                                                                                 |              |

The details of the instruction decode step (or steps) are not shown, since we did not specify the coding of the op-code and we are implementing the controller for only a few instructions. We will show the implementation of the individual instructions, using step numbers beginning at 25.

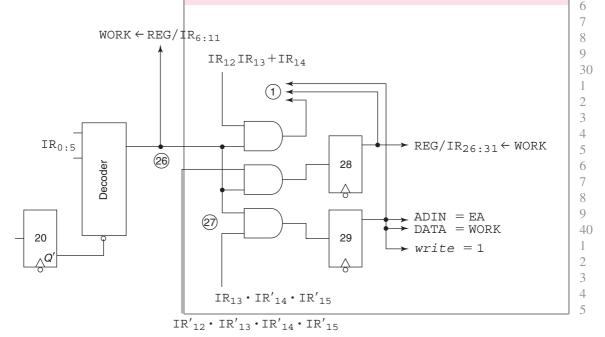

Load register requires only one step, after which it returns to step 1 to fetch a new instruction. On *Store*, the result goes to the register specified by  $IR_{26:31}$  for register addressing  $(IR_{12}' \cdot IR_{13}' \cdot IR_{14}' \cdot IR_{15}')$  and to memory for all other types. Store does not permit immediate addressing; it is treated as a no-op.

### LOD

```

25. REG/IR<sub>6:11</sub> ← WORK; z ← (OR[CPUBUS]';

n ← CPUBUS<sub>0</sub>;

next: 1.

STO

26. WORK ← REG/IR<sub>6:11</sub>.

27. next: 28 (IR<sub>12</sub>' · IR<sub>13</sub>' · IR<sub>14</sub>' · IR<sub>15</sub>'), 1

(IR<sub>12</sub> · IR<sub>13</sub> · IR<sub>14</sub>' · IR<sub>15</sub>'), 29 (else).

```

```

28. REG/IR<sub>26:31</sub> ← WORK;

next: 1.

29. ADIN = EA; DATA = WORK; write = 1;

next: 1.

```

####

Push and Pop are implemented after a decoding branch from step60. Push writes to the location pointed to by the stack pointer and then2decrements the pointer. Pop first increments the stack pointer and then3reads.

5

6

7 8

9

2

3

4

5 6

7

8

0

20

1

2 3

4

5

6

7

8 9

30

1 2

3

4

5

6 7

8

9 40

1

2

3

4

5

10 1

PSH

```

65. ADIN = SP; DATA = REG/IR<sub>6:11</sub>; write = 1.

66. SP ← DEC[SP];

next: 1.

```

POP

67. SP  $\leftarrow$  INC[SP]. 68. ADIN = SP; **read** = 1; REG/IR<sub>6:11</sub>  $\leftarrow$  DATA;  $\mathbf{z} \leftarrow$  (OR[CPUBUS])';  $\mathbf{n} \leftarrow$  CPUBUS<sub>0</sub>; next: 1.

The addition and subtraction instructions are each only one step. The adder has a 33-bit output, the left bit being the carry. Two's complement overflow is detected when two numbers have the same sign  $(INA_0 = INB_0)$  and the result has the opposite sign  $(CPUBUS_0)$ . The expressions for each of the flag bits is the same for almost all instructions.

ADD

```

30. c, \operatorname{REG}/\operatorname{IR}_{6:11} \leftarrow \operatorname{ADD}[\operatorname{REG}/\operatorname{IR}_{6:11}; \operatorname{WORK}; 0];

\mathbf{z} \leftarrow (\operatorname{OR}[\operatorname{CPUBUS}])'; \mathbf{n} \leftarrow \operatorname{CPUBUS}_{0};

\mathbf{v} \leftarrow \operatorname{INA}_{0} \cdot \operatorname{INB}_{0} \cdot \operatorname{CPUBUS}_{0}' + \operatorname{INA}_{0}' \cdot \operatorname{INB}_{0}'

\cdot \operatorname{CPUBUS}_{0};

next: 1.

```

### ADC

- 31. **c**,  $\operatorname{REG}/\operatorname{IR}_{6:11} \leftarrow \operatorname{ADD}[\operatorname{REG}/\operatorname{IR}_{6:11}; WORK;$ **c**];  $\mathbf{z} \leftarrow (\operatorname{OR}[\operatorname{CPUBUS}])'; \mathbf{n} \leftarrow \operatorname{CPUBUS}_{0};$   $\mathbf{v} \leftarrow \operatorname{INA}_{0} \cdot \operatorname{INB}_{0} \cdot \operatorname{CPUBUS}_{0}' + \operatorname{INA}_{0}' \cdot \operatorname{INB}_{0}'$   $\cdot \operatorname{CPUBUS}_{0};$ next: 1.

- 32. **c**, REG/IR<sub>6:11</sub>  $\leftarrow$  ADD[REG/IR<sub>6:11</sub>; WORK'; 1]; **z**  $\leftarrow$  (OR[CPUBUS])'; **n**  $\leftarrow$  CPUBUS<sub>0</sub>; **v**  $\leftarrow$  INA<sub>0</sub>  $\cdot$  INB<sub>0</sub>  $\cdot$  CPUBUS<sub>0</sub>' + INA<sub>0</sub>'  $\cdot$  INB<sub>0</sub>'  $\cdot$  CPUBUS<sub>0</sub>;

next: 1.

```

34. \mathbf{c} \leftarrow ADD_0 [REG/IR_{6:11}; WORK'; 1];

CPUBUS = ADD_{1:32} [REG/IR_{6:11}; WORK'; 1];

\mathbf{z} \leftarrow (OR [CPUBUS])'; \mathbf{n} \leftarrow CPUBUS_0;

\mathbf{v} \leftarrow INA_0 \cdot INB_0 \cdot CPUBUS_0' + INA_0' \cdot INB_0'

\cdot CPUBUS_0;

next: 1.

```

The next two instructions operate on numbers in WORK and ignore the RN field. The results are stored back in either a register or memory, using the steps already implemented for STO.

### INC

СМР

```

36. WORK \leftarrow ADD<sub>1:32</sub>[00000001; WORK;0];

\mathbf{z} \leftarrow (OR[CPUBUS])'; \mathbf{n} \leftarrow CPUBUS_0;

next: 27.

```

### NOT

```

40. WORK \leftarrow WORK'; \mathbf{z} \leftarrow (OR [CPUBUS])';

next: 27.

```

AND uses operands from a register and WORK, storing the result back in that register.

### AND

```

42. REG/IR<sub>6:11</sub> ← REG/IR<sub>6:11</sub> · WORK;

z ← (OR[CPUBUS])'; n ← CPUBUS<sub>0</sub>;

next: 1.

```

The instruction decode step reaches step 43 for all of the shifts and rotates. We assume that the op-code for ASR ends in 00, and ROR ends in 10. We shift one place at a time; step 43 transfers to the step for the store instruction when  $IR_{7:11}$  counts down to 0.  $IR_{7:11} = 00000$  is treated as zero, making these instructions no-ops.

```

43. IR_{7:11} \leftarrow DEC[IR_{7:11}];

next: 44 (OR[IR<sub>7:11</sub>]), 27 (else).

44. next: 45 (IR<sub>4</sub>), 47 (else).

ASR

45. WORK \leftarrow WORK<sub>0</sub>, WORK<sub>0:30</sub>;

z \leftarrow (OR[CPUBUS])';

next: 43.

```

ROR

```

47. WORK \leftarrow WORK<sub>31</sub>, WORK<sub>0:30</sub>;

next: 43.

```

If faster shifting were required, we could build a *barrel shifter*, which would allow a shift of any number of places in one step. The hardware for that is more complex, since each bit of WORK could be loaded with any other bit or with 0. In contrast, the implementation we have shown only requires that each bit be loaded with the bit on either side (or 0 for the first and last bits).

The conditional jump and call instructions depend on the variable **br**, where

$$\mathbf{br} = OR[DCD(IR_{8:11}) \cdot (\mathbf{z}, \mathbf{z}', \mathbf{n}, \mathbf{n}', \mathbf{c}, \mathbf{c}', \mathbf{v}, \mathbf{v}', 0, 0, 0, 0, 0, 0, 0, 0, 1)]$$

DCD is a decoder with four inputs and 16 outputs, one of which is 1. That is ANDed with the 16-bit vector with each of the conditions, as specified in Table 10.1. Thus, **br** is 1 if the specified branch condition is satisfied and 0, otherwise. (Unused codes are treated as never branch. They could be treated as an unconditional branch by changing all of the 0's to 1's.)

On jump, the program counter is loaded with the effective address if the condition is met; otherwise, it returns to step 1. On a successful call, the contents of the program counter are first pushed onto the stack and then the effective address is moved to the PC.

### JMP

```

50. br: PC \leftarrow EA;

next: 1.

```

### CLL

51. next: 1 (br), 52 (else)

52. ADIN = SP; DATA = PC; write = 1.

53. SP ← DEC[SP].

54. PC ← EA;

next: 1.

Finally, the return from subroutine (unconditional) pops the address from the stack and loads that into the program counter.

### RTS

| 2<br>3                 | Add a new instruction to decrement the register pointed to by the RN field<br>and jump to the address if the result is 0. (This is a loop control instruction.)<br>The simplest way is to do the addressing and jump to step 55 from<br>step 20.                                                                                                                                                                                                | EXAMPLE 10.5 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| 6                      | 55. WORK ← REG/IR <sub>6.11</sub> .                                                                                                                                                                                                                                                                                                                                                                                                             |              |

| 7                      | 56. $\operatorname{REG}/\operatorname{IR}_{6:11} \leftarrow \operatorname{ADD}_{1:32}[FFFFFFFF; WORK; 0];$                                                                                                                                                                                                                                                                                                                                      |              |

| 8                      | next: 1 (OR[CPUBUS]), 57 (else).                                                                                                                                                                                                                                                                                                                                                                                                                |              |

| 9                      | 57. PC $\leftarrow$ EA;                                                                                                                                                                                                                                                                                                                                                                                                                         |              |

| 10<br>1                | next: 1.                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

| 2<br>3<br>4<br>5<br>6  | Since step 57 is identical to step 54, the branch at step 56 could go to 54,<br>eliminating step 57. It was necessary to move the register to WORK (step<br>55) because the bus structure up until this point put both the register and<br>the constant on INA. If the bus structure were modified, we could<br>combine steps 55 and 56.                                                                                                        |              |

| 9<br>20<br>1<br>2      | Add a new instruction, <i>Stack add</i> . It adds the top two entries on the stack<br>and pushes the answer back onto the stack. The operands are destroyed.<br>No flags are involved.<br>This requires and additional register, WORK2, to store the second<br>number. (That register would be needed by more complex instructions,<br>such as <i>Multiply</i> . We pop the two operands, add them, and then push the<br>result onto the stack. | EXAMPLE 10.6 |

| 5                      | 80. SP ← INC[SP].                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| 6                      | 81. ADIN = SP; read = 1; WORK $\leftarrow$ DATA.                                                                                                                                                                                                                                                                                                                                                                                                |              |

| 7                      | 82. SP $\leftarrow$ INC[SP].                                                                                                                                                                                                                                                                                                                                                                                                                    |              |

| 8<br>9                 | 83. ADIN = SP; read = 1; WORK2 $\leftarrow$ DATA.                                                                                                                                                                                                                                                                                                                                                                                               |              |

| 30                     | 84. WORK $\leftarrow$ ADD <sub>1:32</sub> [WORK2; WORK; 0].                                                                                                                                                                                                                                                                                                                                                                                     |              |

| 1                      | 85. ADIN = SP; DATA = WORK; write = 1.                                                                                                                                                                                                                                                                                                                                                                                                          |              |

| 2<br>3                 | 86. SP ← INC[SP];                                                                                                                                                                                                                                                                                                                                                                                                                               |              |

| 4                      | next: 1.                                                                                                                                                                                                                                                                                                                                                                                                                                        |              |

| 6<br>7<br>8<br>9<br>40 | Modify <b>br</b> so as to provide conditional branches for comparing two signed<br>and unsigned numbers.<br>Two numbers can be compared by subtracting them and then using a<br>conditional jump. The comparisons are between the number in the register<br>(REG/IR <sub>6:11</sub> ), <i>a</i> , compared with the number specified by the address, <i>b</i> .<br>There are separate tests for signed and unsigned numbers based on the        |              |

| 1<br>2<br>3<br>4<br>5  | flag bits.                                                                                                                                                                                                                                                                                                                                                                                                                                      |              |

|              | For signed numbers, when $a < b$ , the result is negative unless there is<br>overflow. Thus, the condition is $\mathbf{n} \oplus \mathbf{v}$ . For less than or equal, we have<br>$\mathbf{z} + \mathbf{n} \oplus \mathbf{v}$ . The opposite of less than is greater than or equal, $(\mathbf{n} \oplus \mathbf{v})'$ , and greater than is the complement of less than or equal, $\mathbf{z} + \mathbf{n} \oplus \mathbf{v}$ .<br>For unsigned numbers, $a < b$ is indicated by $\mathbf{c}'$ , less than or equal by<br>$\mathbf{c}' + \mathbf{z}$ , greater than by $(\mathbf{c}' + \mathbf{z})'$ , and greater than or equal by $\mathbf{c}$ .<br>If the following codes are added to the list in Table 10.1,<br>1000 < (After SUB for signed numbers)<br>$1001 \le$<br>$1010 \ge$<br>1011 ><br>$1100 \le (\text{After SUB for unsigned numbers})$<br>1101 > |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | then the definition of <i>br</i> becomes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|              | $\mathbf{br} = OR[DCD(IR_{8:11}) \cdot (\mathbf{z}, \mathbf{z}', \mathbf{n}, \mathbf{n}', \mathbf{c}, \mathbf{c}', \mathbf{v}, \mathbf{v}', \mathbf{n} \oplus \mathbf{v}, \mathbf{z} + \mathbf{n} \oplus \mathbf{v}, (\mathbf{n} \oplus \mathbf{v})', (\mathbf{z} + \mathbf{n} \oplus \mathbf{v})', \mathbf{c}' + \mathbf{z}, \mathbf{c} \cdot \mathbf{z}', 0, 1)]$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| EXAMPLE 10.8 | Include a new instruction to add a set of numbers stored in consecutive memory locations. The address field specifies the location of the first number. The register specified by RN contains the size of the set (how many numbers to be added) and is replaced by the sum. The flag bit <b>c</b> is set to one iff any of the additions produced unsigned overflow.<br>Step 20 branches to step 90. We need three registers, in addition to EA, in this process: one to hold the count, one to hold the sum as we are adding, and one to hold each new number as it is read. One approach is to store the sum in the register and the count in WORK. The additional register, WORK2, would be connected to INB. (Note that this is a different connection from Example 10.6.)                                                                                  |